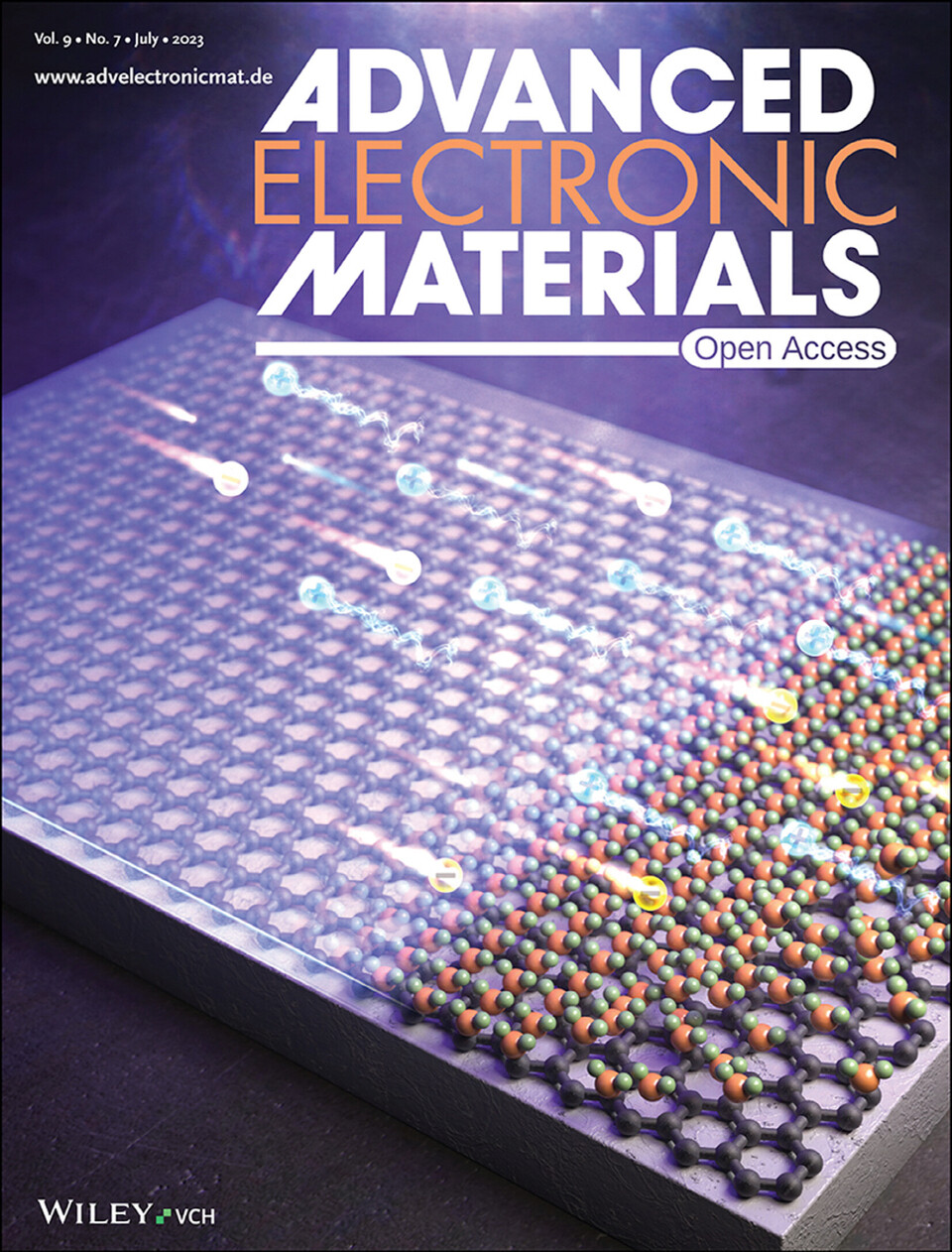

포스텍(포항공과대학교, 총장 김무환) 기계공학과 안지환 교수, 싱가포르 난양공대 기계공학과 신정우 박사, 서울과학기술대학교 MSDE(생산시스템·설계공학)학과 박건우 연구원 공동 연구팀은 그래핀 전극 표면에 직접 개발한 자외선 보조 원자층 증착 공정(이하 UV-ALD)을 적용하여 고품질의

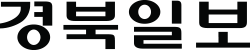

이번 연구에서 연구팀은 최초로 2차원 소재인 그래핀 표면 유전막 증착 공정에 UV-ALD를 적용했다. ‘원자층 증착 공정(Atomic layer deposition, 이하 ALD)’은 기판에 원자층 단위로 두께가 제어되는 매우 균일하고 얇은 막을 입히는 방법으로, 최근 반도체 소자의 미세화에 따라 중요성 및 활용도가 급격히 상승하고 있다. 이 공정에 자외선을 결합한 UV-ALD은 기존 ALD에 비해 치밀한 유전막 증착이 가능하다고 알려져 있으나, 그래핀과 같은 2차원 소재 가공 공정에 적용된 사례는 없었다.

연구팀은 그래핀 표면상 원자층 유전막 증착 시 저에너지(10 eV2)이하) 자외선을 조사해주며 공정을 진행했다. 그 결과, 특정 조건(공정 사이클당 5초 이내)에서 특성 저하 없이 그래핀 표면을 활성화시킴과 동시에 저온(섭씨 100도 이하)에서도 고밀도 · 고순도 원자층 유전막 증착이 가능함을 입증했다.

연구를 이끈 안지환 교수는 “자외선과 결합된 원자층 유전막 증착 공정을 이용해 고품질의 그래핀-유전막 계면을 형성할 수 있었다”며, “2차원 소재 특성 저하없이 균일한 원자층 유전막을 증착한 이번 연구 결과가 향후 2차원 소재 기반의 차세대 반도체 소자 및 에너지 소자 공정 개발에 도움이 되길 바란다”는 기대를 전했다.

한편, 이 연구는 한국연구재단의 대학중점연구소지원사업, 중견연구자지원사업, 산업통상자원부의 나노융합산업핵심기술개발사업의 지원으로 진행됐다.